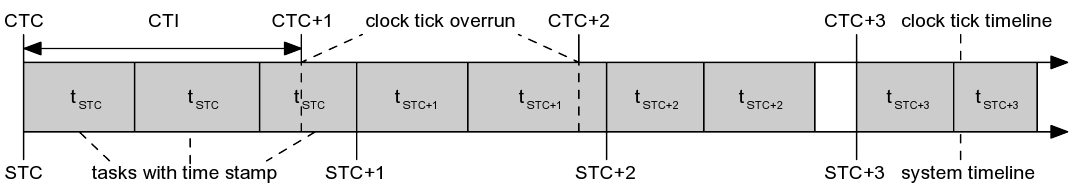

In reference to an underlying DE model of computation and additional real-time conditions, the RTOS includes two separate timelines.

First, an external clock tick timeline of a configured clock tick interval (CTI) determines the global system clock pulse. A corresponding clock tick counter (CTC) is incremented each time a clock tick occurred.

Secondly, an internal system time counter (STC) is used as time base for EventQ entries. To ensure a quasi-zero-delayed execution behavior of FSM instances, the STC is not updated until all scheduled synchronous events for this timestamp are processed.

While the scheduler is able to perform all tasks, related to a specific system timestamp, within one clock tick period, both timelines are running synchronously. Otherwise, in case processing of all events, scheduled for the current internal system time, exceeds the CTI limit, a clock tick overrun occurs and given real-time conditions might be violated. In a soft real-time system, a clock tick overrun might be ignorable, but in case of hard real-time conditions, the application usually has to be aborted and reconfigured with a longer clock tick interval. To define consequences of a real-time violation, the generator output provides a configurable handler function, which is called whenever the defined real-time level could not be met.

The figure below shows an example soft real-time scenario with the time response of both RTOS timelines. All RTOS timeline related configuration units are described in detail in the Porting section.